# SONY

# CXA2016S

# Sync Identification for CRT Display

#### Description

The CXA2016S is used for sync signal identification and waveform shaping in the CRT computers display for multi-scan system. There are three types of sync input signals for identification: separate sync, composite sync, and sync on video signals.

# Features

- Power save function available (5 V power supply)

- Clamp pulse output position selectable among sync interval, back porch interval, and AUTO.

- Polarity information of sync signals is output.

- Polarity and amplitude of input signals:

|                   | Polarity          | Amplitude (Vp-p) |

|-------------------|-------------------|------------------|

| V. separate sync: | Positive/Negative | 1 to 5           |

| H. separate sync: | Positive/Negative | 1 to 5           |

| Composite sync:   | Positive/Negative | 1 to 5           |

| Sync on video:    |                   |                  |

| Sync signals par  | t of Negative     | 0.2 to 0.4       |

| Video part        |                   | 0 to 1.4         |

# Absolute Maximum Ratings (Ta=25°C)

| <ul> <li>Supply voltage</li> </ul>        | Vcc  | 12          | V  |

|-------------------------------------------|------|-------------|----|

| <ul> <li>Operating temperature</li> </ul> | Topr | -20 to +75  | °C |

| <ul> <li>Storage temperature</li> </ul>   | Tstg | -65 to +150 | °C |

| Allowable power dissipation               | on   |             |    |

|                                           | Pd   | 962         | mW |

| Operating Conditions                      |      |             |    |

| Operating Conditions                      |      |             |    |

# Supply voltage Vcc $5 \pm 0.25$ V

# Applications

CRT display monitor

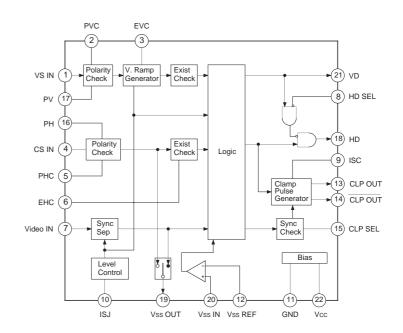

# Pin Configuration (Top View)

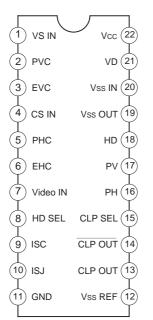

# **Block Diagram**

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

-1-

# **Pin Description**

(Ta=25 °C, Vcc=5 V)

| Pin<br>No | Symbol | Pin<br>voltage | Equivalent circuit                               | Description                                                                                                                                                                                                                                                                                                                                                            |

|-----------|--------|----------------|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1         | VS IN  | 2.6 V          | 100 ↓ Vcc<br>↓ 1k ↓ Vcc<br>↓ 100 ↓ ↓ ↓ GND       | V. separate sync (positive/negative<br>polarity) as capacitor input. Amplitude<br>is 1 to 5 Vp-p.                                                                                                                                                                                                                                                                      |

| 2         | PVC    |                | 2                                                | This pin connects a 0.22 µF<br>integrating capacitor for the vertical<br>signal polarity check circuit to GND.<br>When connecting the capacity at<br>positive polarity, it is 2.9 V and at<br>negative polarity, 120 mV.                                                                                                                                               |

| 3         | EVC    |                | 200≷200<br>↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ | V. ramp waveforms generation part of<br>vertical signal exist check circuit.<br>Generates ramp waveforms<br>synchronously with the input signal<br>cycle and connects 0.22 µF to GND.                                                                                                                                                                                  |

| 4         | CS IN  | 2.6 V          | 4<br>GND                                         | Inputs composite sync<br>(positive/negative polarity) and H.<br>separate sync (positive/negative<br>polarity) as capacitor input. Amplitude<br>is 1 to 5 Vp-p.                                                                                                                                                                                                         |

| 5         | РНС    |                |                                                  | This pin connects a 0.1 $\mu$ F integrating capacitor for the horizontal signal polarity check circuit to GND. When connecting the capacity at positive polarity, it is 2.6 V and at negative polarity, 350 mV.                                                                                                                                                        |

| 6         | EHC    |                | 6                                                | A 33 k $\Omega$ resistance and a nearly peak<br>hold circuit for 0.22 µF capacitor are<br>connected to this pin for input signal<br>exist check at CS IN input pin. When<br>a signal is input at CS IN pin, a nearly<br>peak hold is executed at 2.1 V to 2.7<br>V, a comparison is made with the 1.4<br>V reference voltage, and input signal<br>exist is identified. |

—2—

| Pin     | Symbol   | Pin     | Equivalent circuit                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------|----------|---------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No<br>7 | Video IN | voltage | ₹2k<br>Vcc<br>T<br>GND                    | Inputs sync on video (sync at negative polarity). Connects in series a 1 $\mu$ F capacitor and a 270 $\Omega$ resistance to input signals.                                                                                                                                                                                                                                                                                                 |

| 8       | HD SEL   |         | B<br>1k<br>GND                            | Selects output processing of HD<br>(H. Drive Pulse) at a VD interval.<br>Input at TTL level.<br>When Low level is selected, HD is not<br>output at a VD interval.<br>When High level is selected, HD is<br>output at the VD interval.                                                                                                                                                                                                      |

| 9       | ISC      | 1.2 V   | 9 $100$ $50k$ $GND$                       | Resistance connecting pin for<br>reference current source of clamp<br>pulse output circuit, and connects 12<br>$k\Omega$ resistance to GND. When a 12 $k\Omega$<br>resistance is connected, a 100 $\mu$ A<br>current flows through this pin (pulse<br>width is approximately 300 ns).<br>Clamp pulse output pulse width is<br>varied by changing the value of the<br>resistance.<br>*Use a metal film resistor with an<br>accuracy of ±1 % |

| 10      | ISJ      | 1.2 V   | $10$ $4k \leq 1k$ $Vcc$<br>10 $50k$ $GND$ | Resistance connecting pin for<br>reference current source and<br>connecting 12 k $\Omega$ resistance to GND.<br>When the resistance is connected, a<br>100 $\mu$ A current flows through this pin.<br>*Use a metal film resistor with an<br>accuracy of ±1 %                                                                                                                                                                               |

| 11      | GND      | 0 V     |                                           | GND pin.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 12      | Vss REF  | 3.125 V | Vcc<br>12<br>12<br>1k<br>20k<br>GND       | Reference pin for V. sync separator of composite sync and video sync.                                                                                                                                                                                                                                                                                                                                                                      |

| Pin      |          | Pin     |                                                                                              |                                                                                                                                                                                                                                                                                                      |

|----------|----------|---------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No       | Symbol   | voltage | Equivalent circuit                                                                           | Description                                                                                                                                                                                                                                                                                          |

| 13       | CLP OUT  |         | Vcc                                                                                          | Clamp pulse output; Open collector-<br>type pin at positive polarity.                                                                                                                                                                                                                                |

| 14       | CLP OUT  | _       | 13                                                                                           | Clamp pulse output; Open collector-<br>type pin at negative polarity.                                                                                                                                                                                                                                |

| 15       | CLP SEL  |         | Vcc<br>30k<br>15<br>↓<br>1k<br>↓<br>↓<br>↓<br>↓<br>↓<br>↓<br>↓<br>↓<br>↓<br>↓<br>↓<br>↓<br>↓ | Selects output position of a clamp<br>pulse. Input at TTL level.<br>When Low level is selected, a clamp<br>pulse is output at a back porch<br>interval.<br>When High level is selected, clamp<br>pulse is output at a sync interval.<br>See the Description of Operation for<br>Input/Output Matrix. |

| 16<br>17 | PH<br>PV |         | 20k<br>16<br>↓<br>20k<br>GND                                                                 | Output polarity information of<br>horizontal and vertical sync signals.<br>See the Description of Operation for<br>Input/Output Matrix.                                                                                                                                                              |

| 18       | HD       |         | 18<br>↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓                                                  | HD (H. Drive Pulse) output; Push-pull<br>type pin at positive polarity.                                                                                                                                                                                                                              |

| 19       | Vss OUT  |         | 19<br>↓ 2.5k<br>↓ 17.5k<br>GND                                                               | Composite sync or sync signal<br>separated from video sync is output.<br>Output is at positive polarity.                                                                                                                                                                                             |

| 20       | Vss IN   |         | 20<br>1k<br>GND                                                                              | Input for V. sync separator<br>comparator. Integrates the output at<br>Pin 19 and inputs it.                                                                                                                                                                                                         |

—4—

| Pin<br>No | Symbol | Pin<br>voltage | Equivalent circuit                            | Description                                                        |

|-----------|--------|----------------|-----------------------------------------------|--------------------------------------------------------------------|

| 21        | VD     |                | 21<br>Vcc<br>Vcc<br>Vcc<br>Vcc<br>Slok<br>GND | VD (V. Drive Pulse) output pin.<br>Output is at positive polarity. |

| 22        | Vcc    | 5 V            | _                                             | Power supply pin.                                                  |

| No. | Item                       | Symbol | Measurement contents                                                                                                                                                                           | Measurement<br>point          | Min.   | Тур.                                | Max.       | Unit |

|-----|----------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--------|-------------------------------------|------------|------|

| 1   | VD output<br>voltage       | Evd    | Measure VD output peak value<br>during V. separate sync input.<br>Input signal A. (tw=60 µs)                                                                                                   | VD<br>(Pin 21)                | 4.3    | ligh leve<br>4.9<br>.ow leve        |            | V    |

|     |                            |        | Measure HD output peak value                                                                                                                                                                   |                               | —<br>+ | 0.1<br>ligh leve                    | 0.4        |      |

| 2   | HD output<br>voltage       | Енр    | during sync on video input.<br>Input signal C. (tw=1 µs)                                                                                                                                       | HD<br>(Pin 18)                | 3.3    | 4.2<br>-ow leve                     |            | V    |

|     | Clamp pulse                |        | Measure clamp pulse output peak value during composite sync input.                                                                                                                             | CLAMP<br>(Pin 13)             | 4.3    | ligh leve<br>4.9<br>.ow leve<br>0.3 | el         | V    |

| 3   | output voltage             | Еср    | Input signal Β. (tw=1 μs)                                                                                                                                                                      | CLAMP<br>(Pin 14)             | 4.3    | ligh leve<br>4.9<br>Low leve        |            | V    |

|     | Clamp pulse                |        | Measure clamp pulse output pulse width during composite sync input.                                                                                                                            | CLAMP<br>(Pin 13)             | 260    | 0.4<br>305                          | 0.9<br>380 | ns   |

| 4   | output pulse<br>width      | tc     | Input signal B. (tw=1 µs)                                                                                                                                                                      | CLAMP<br>(Pin 14)             | 260    | 310                                 | 380        | ns   |

| 5   | HD delay                   | thd    | Measure delay difference between<br>CS and HD during composite sync<br>input. Or the time from CS<br>(positive polarity) rise time (50 %)<br>to HD output rise time (50 %).<br>Input signal D. | HD<br>(Pin 18)                |        | 75                                  | 100        | ns   |

| 6   | Clamp pulse                | tcd1   | Measure delay difference between<br>HD and clamp pulse during<br>composite sync input. Or the time                                                                                             | CLAMP<br>(Pin 13)             | _      | 5.0                                 | 30         | 20   |

| 0   | delay                      |        | from HD output fall time (50 %) to<br>clamp pulse output rise time <sup>*1</sup> (50<br>%). Input signal B.                                                                                    | CLAMP<br>(Pin 14)             | _      | 5.0                                 | 30         | ns   |

| 7   | Polarity<br>identification | PN     | Sync signal polarity information<br>is output.<br>Measure high level voltage.<br>(No load)                                                                                                     | PH, PV<br>(Pins 16<br>and 17) | 4.3    |                                     |            | V    |

| ,   | output voltage             | PP     | Sync signal polarity information<br>is output.<br>Measure low level voltage.<br>(No load)                                                                                                      | PH, PV<br>(Pins 16<br>and 17) |        |                                     | 0.4        | V    |

| 8   | Current consumption        | Icc    | Vcc=5 V. Measure current consumption during no signal input.                                                                                                                                   | Vcc<br>(Pin 22)               | _      | 26.5                                | 45         | mA   |

# Electrical Characteristics (Ta=25 °C, Vcc=5 V. See the Electrical Characteristics Measurement Circuit.)

\*1 CLAMP is for the fall time.

# **Types of Signal Source**

| Signal | Item    | V. SYNC IN (Pin 1)                                    | Composite SYNC IN (Pin 4)                                                                                                                                             | Video IN (Pin 7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------|---------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A      | 1       | fv=40 Hz<br>twv=60 μs<br>1wv Negative logic<br>1 Vp-p |                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| В      | 3, 4, 6 |                                                       | ∨         fv=40 Hz           ↓         twv=60 µs           1wv         1 Vp-p           H         fH=50 kHz           ↓         twH=1 µs           1WH         1 Vp-p |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| С      | 2       |                                                       |                                                                                                                                                                       | V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.2V<br>$60\mu s$<br>fv=40 Hz<br>$twv=60 \ \mu s$<br>H<br>$15\mu s$<br>$15\mu s$<br>10H<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V<br>0.7V |

| D      | 5       |                                                       | fн=50 kHz<br>twн=1 µs<br>Positive logic 1 Vp-p                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

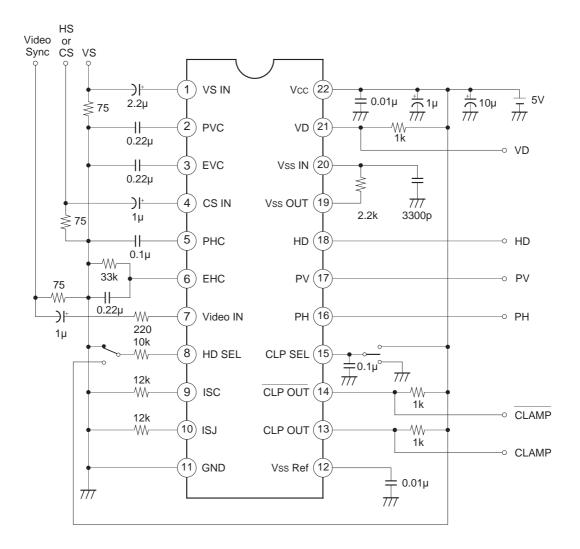

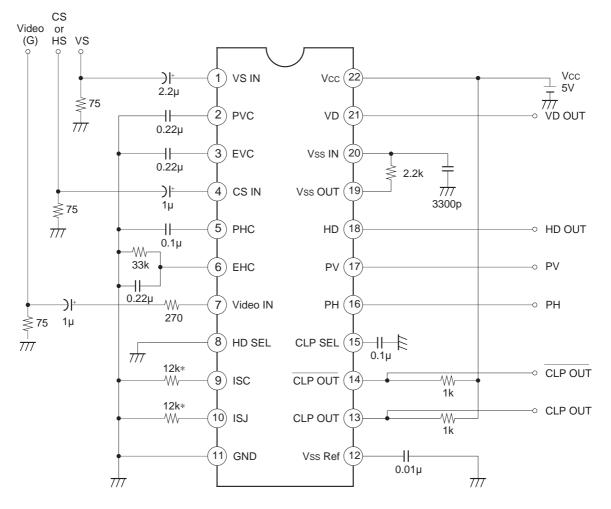

# **Electrical Characteristics Measurement Circuit**

# Description of Operation

Input signal

- VS IN (Pin 1)

- fv : 40 to 200 Hz

- Vs : 1 to 5Vp-p (positive/negative polarity)

- HS IN (Pin 4)

- fн : 15k to 130 kHz

- Vs : 1 to 5 Vp-p (positive/negative polarity)

- CS IN (Pin 4)

- fн : 15 k to 130 kHz

- fv : 40 to 200 Hz

- Vs : 1 to 5 Vp-p (positive/negative polarity)

- Video IN (Pin 7)

- fн : 15 k to 130 kHz

- $fv\ :\ 40$  to 200 Hz

- $Vv\ :\ 0$  to 1.4 Vp-p

- Vs : 0.2 to 0.4 Vp-p

Clamp Pulse Output

• Clamp pulse (Pins 13 and 14) is output under the following conditions.

Pin 13 is for open collector output and is at positive polarity.

Pin 14 is for open collector output and is at negative polarity.

td: Clamp pulse delays for 10 to 20 ns from HD.

tw: Clamp pulse width varies depending on the value of the resistance connected to Pin 9.

<Conditions>

- (1) When CS IN or Video IN is selected, a clamp pulse at the VD interval is not output.

- (2) During H./V. Separate Sync, a clamp pulse at the VD interval is also output.

- (3) When Pin 15 (CLP SEL) is connected to GND, a clamp pulse is output at the back porch interval. When Pin 15 (CLP SEL) is connected to Vcc, a clamp pulse is output at the SYNC interval. If a capacitor is connected between this pin and GND, the output position is automatically selected.

| CLP SEL | VS IN | CS IN | Video IN | Clamp pulse output position |

|---------|-------|-------|----------|-----------------------------|

| GND     | *     | *     | *        | Back porch interval         |

| Vcc     | *     | *     | *        | SYNC interval               |

|         | *     | —     | 0        | Back porch interval         |

| AUTO    | *     | 0     | _        | SYNC interval               |

|         | *     |       |          | (Back porch interval)       |

Clamp Pulse Input/Output Matrix

[O] indicates that input SYNC exists.

[--] indicates no signal (no SYNC).

[\*] has no relation with input signal.

**HD Select Function**

When HD SEL is Low, HD at the VD interval is not output. When HD SEL is High, HD at the VD interval is output.

During separate sync output, HD is output regardless of HD SEL.

# Mode Matrix of SYNC Polarity Identification Signal

| VS IN                  | CS IN                    | PV out   | PH out   |

|------------------------|--------------------------|----------|----------|

| (Pin 1)                | (Pin 4)                  | (Pin 17) | (Pin 16) |

|                        | No signal                | Low      | Low      |

| VS (positive polarity) | HS (positive polarity)   | Low      | Low      |

|                        | HS (negative polarity)   | Low      | High     |

|                        | No signal                | High     | Low      |

| VS (negative polarity) | HS (positive polarity)   | High     | Low      |

|                        | HS (negative polarity)   | High     | High     |

|                        | No signal                | Low      | Low      |

| No signal              | COMP (positive polarity) | Low      | Low      |

|                        | COMP (negative polarity) | Low      | High     |

Low level: 0 to 0.4 V, High level: Vcc

#### Input/Output Matrix

| VS IN | CS IN | Video IN | VD OUT  | HD OUT  |

|-------|-------|----------|---------|---------|

| 0     | 0     | *        | VS      | CS      |

| _     | 0     | *        | CS      | CS      |

| _     |       | 0        | Video   | Video   |

| _     |       |          | (Video) | (Video) |

| 0     | _     | 0        | VS      | Video   |

| 0     |       |          | VS      | (Video) |

Note) The corresponding sync signals are input to VSIN and Video IN.

[O] indicates that input SYNC exists.

[--] indicates no signal.

[\*] has no relation with input signal.

# **Application Circuit**

Use metal film resistor with an accuracy of  $\pm 1\%$  for the resistor marked \*.

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

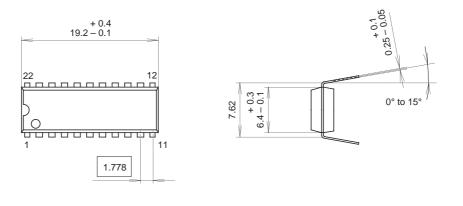

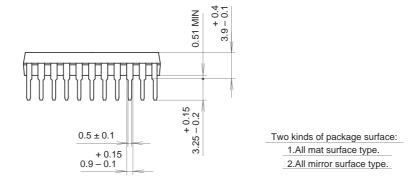

Package Outline Unit : mm

22PIN SDIP (PLASTIC)

# PACKAGE STRUCTURE

| SONY CODE  | SDIP-22P-01    |

|------------|----------------|

| EIAJ CODE  | SDIP022-P-0300 |

| JEDEC CODE |                |

| MOLDING COMPOUND | EPOXY RESIN    |

|------------------|----------------|

| LEAD TREATMENT   | SOLDER PLATING |

| LEAD MATERIAL    | COPPER ALLOY   |

| PACKAGE MASS     | 0.95g          |